# MPC8572EAMC Advanced Mezzanine Card User Guide

MPC8572EAMCUG Rev. 1.2 11/2008

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. RapidIO is a registered trademark of the RapidIO Trade Association. IEEE 1149.1 and 1588 are trademarks or registered trademarks or registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Document Number: MPC8572EAMCUG Rev. 1.2, 11/2008

## Contents

Paragraph Number

Title

Page Number

#### Contents iii

#### Chapter 1 General Information

| 1.1   | Introduction                             | 1-1 |

|-------|------------------------------------------|-----|

| 1.2   | Working Configuration                    | 1-1 |

| 1.2.1 | System Development Configuration         | 1-1 |

| 1.3   | MPC8572EAMC Processor Board              |     |

| 1.3.1 | External Connectors                      | 1-3 |

| 1.4   | MPC8572EAMC Block Diagram                | 1-6 |

| 1.5   | Definitions, Acronyms, and Abbreviations | 1-6 |

| 1.6   | Related Documentation                    | 1-7 |

| 1.7   | Specifications                           | 1-7 |

### Chapter 2 Hardware Preparation and Installation

| 2.1 | Unpacking Instructions    | 2- | 1 |

|-----|---------------------------|----|---|

| 2.2 | Installation Instructions | 2- | 1 |

### Chapter 3 Memory Map

#### Chapter 4 Controls and Indicators

| 4.1 | DIP Switch Settings | 4-2 |

|-----|---------------------|-----|

| 4.2 | Jumpers             | 4-3 |

| 4.3 | LEDs                | 4-4 |

| 4.4 | Headers             | 4-5 |

| 4.5 | Push Buttons        | 4-5 |

### Chapter 5 MPC8572EAMC Functional Description

| • |

|---|

## Contents

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| 5.1.3               | PCI-Express Interface                              |                |

| 5.1.4               | Local Bus Interface                                |                |

| 5.1.4.1             | MPC8572E Interrupts                                |                |

| 5.1.5               | MPC8572E DUART1/2                                  |                |

| 5.1.6               | COP/JTAG Debug Interface                           | 5-11           |

| 5.1.7               | MPC8572E Power-On Reset Configuration (POR Config) |                |

| 5.2                 | MPC8572EAMC Ethernet Connectivity                  |                |

| 5.3                 | Clocking                                           |                |

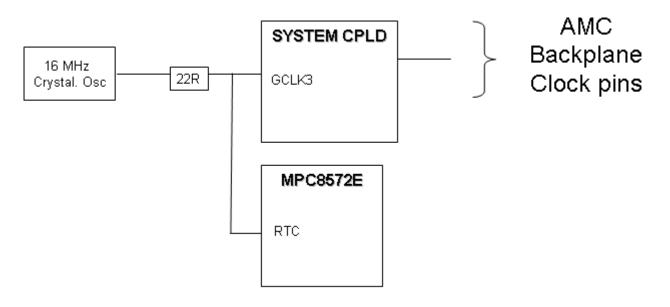

| 5.3.1               | MPC8572EAMC System Clock (SYSCLK)                  | 5-19           |

| 5.3.2               | MPC8572EAMC Real Time Clock (RTC)                  |                |

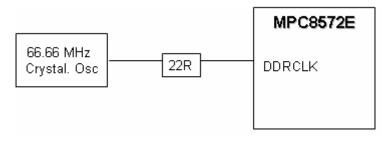

| 5.3.3               | MPC8572EAMC DDR Clock (DDRCLK)                     |                |

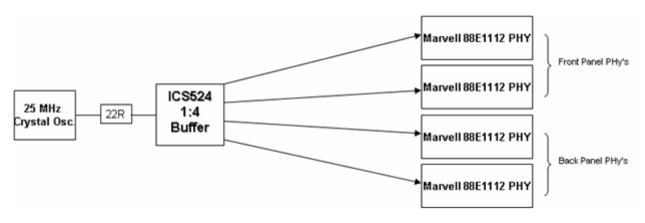

| 5.3.4               | SGMII Gigabit Ethernet PHY Clocks                  | 5-21           |

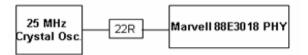

| 5.3.5               | FEC 10/100 Ethernet PHY Clock                      |                |

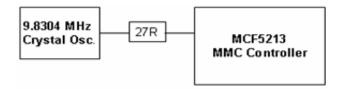

| 5.3.6               | MMC Clock—ColdFire MCF5213 (EXTAL)                 |                |

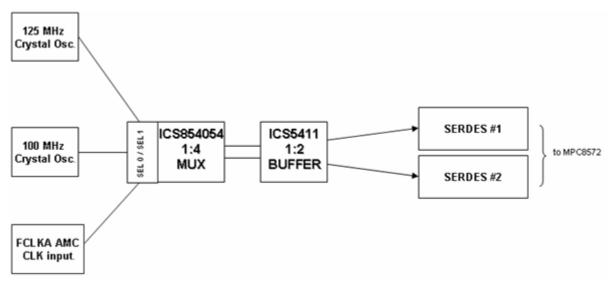

| 5.3.7               | MPC8572EAMC SERDES LVDS Clock (100/125MHZ)         |                |

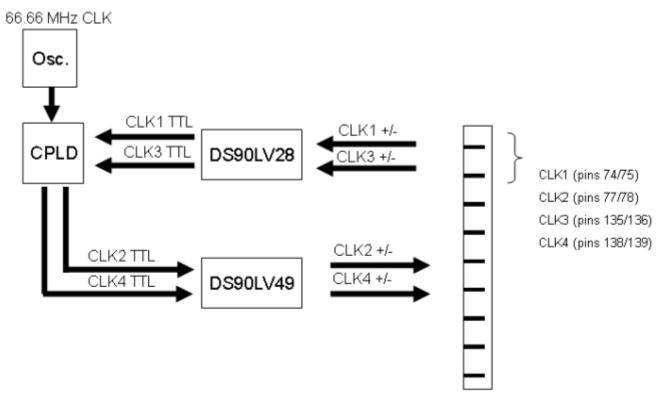

| 5.3.8               | MPC8572EAMC Clock Port Region                      |                |

| 5.4                 | General Board Configuration                        | 5-23           |

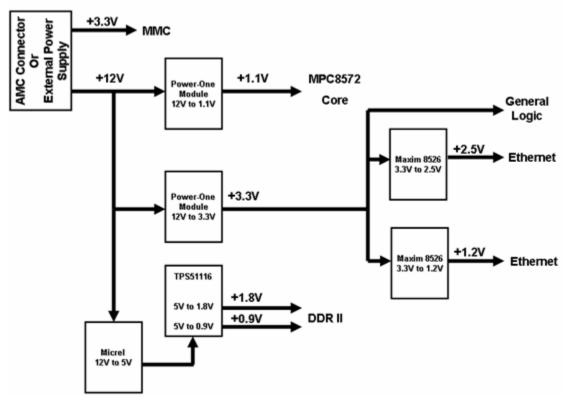

| 5.4.1               | MPC8572EAMC Power                                  |                |

| 5.4.1.1             | MPC8572EAMC Voltage Requirements                   |                |

| 5.4.1.2             | Power Supply Distribution                          | 5-25           |

| 5.4.1.3             | Voltage Regulator Configuration                    | 5-25           |

| 5.4.1.3.1           | MPC8572EAMC Board Headers                          |                |

| 5.4.2               | Board CPLD Logic/POR Configuration                 |                |

| 5.5                 | AdvancedMC Backplane Connector                     |                |

| 5.6                 | MMC Control                                        |                |

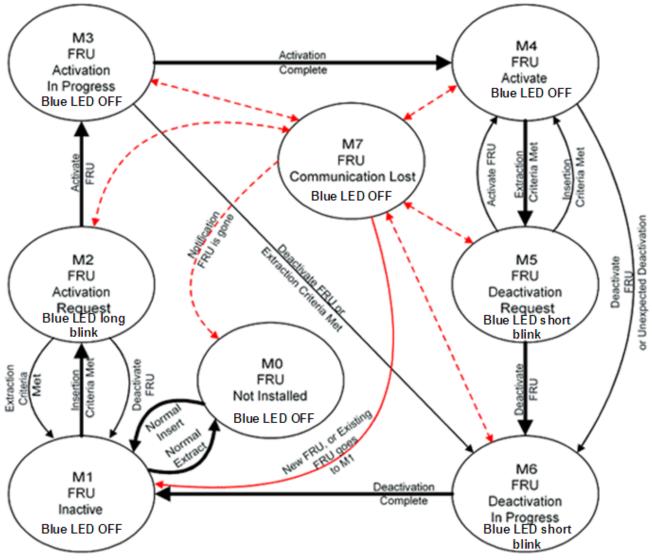

| 5.6.1               | MMC Operation Overview                             | 5-39           |

| 5.6.1.1             | Module Insertion                                   |                |

| 5.6.1.2             | Enabling the MMC                                   | 5-39           |

| 5.6.1.3             | Status LEDS                                        |                |

| 5.6.1.4             | Hot Swap Switch                                    | 5-40           |

| 5.6.1.5             | Module Management Communications Bus (IPMB-L)      | 5-41           |

| 5.6.1.6             | Geographical Address (GA[2:0])                     | 5-41           |

| 5.6.1.7             | Module temperature Sensors                         | 5-41           |

| 5.6.1.8             | Module Voltage Sensors                             |                |

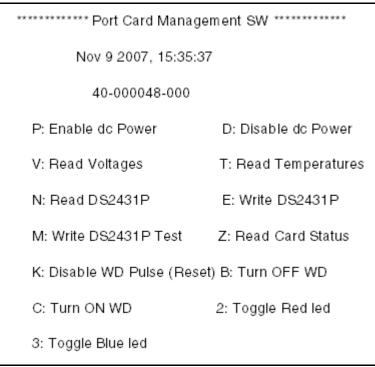

| 5.6.1.9             | MMC UART                                           |                |

| 5.6.1.10            | BDM Debug Header                                   |                |

| 5.6.1.11            | Persistent Store                                   |                |

| 5.6.2               | MMC User Operation                                 |                |

| 5.6.2.1             | Hot Swapping                                       |                |

| 5.6.2.2             | UART Terminal                                      |                |

| 5.6.2.3             | FRU records                                        |                |

## Contents

| Paragraph<br>Number | Title                | Page<br>Number |

|---------------------|----------------------|----------------|

| 5.7                 | Thermal Requirements |                |

Appendix A Revision History

## Contents

Paragraph Number

Title

Page Number

## Chapter 1 General Information

## 1.1 Introduction

This document describes the MPC8572EAMC AdvancedMC (AMC). The MPC8572EAMC provides an AdvancedMC debugging platform for engineers developing applications for the MPC8572E series of Freescale Processors.

The MPC8572E family of processors is designed to offer clock speeds from 1.2 GHz up to 1.5 GHz, combining two powerful e500 processor cores, enhanced peripherals and high-speed interconnect technology to balance processor performance with I/O system throughput. These processors also include a next-generation double data rate (DDR2/DDR3) memory controller, enhanced Gigabit Ethernet support, double precision floating point and an integrated security engine that features updated advanced encryption standard (AES) functionality.

The MPC8572EAMC single-width AdvancedMC board is designed around the dual-core feature set of the MPC8572E microprocessor. Each integrated 32-bit wide DDR2/3 controller connects to a separate 1-GByte DDR2 SoCDIMM (2 GBytes in total). For control plane applications, two SGMII Ethernet ports are connected to AdvancedMC ports 0 and 1. The other two SGMII Ethernet ports of the MPC8572E are connected to the front panel of the card, as well as an additional 10/100 Fast Ethernet port. A dual USB debug port and board reset switch, are also connected to the front card panel.

128 Mbytes of FLASH memory is available on the AdvancedMC for file/OS storage. AdvancedMC board management is handled via a CorEdge<sup>TM</sup>-enabled module management controller based around a Freescale MCF5213. This provides the board with power sequencing, hot swap functionality, temperature sensing, and FRU record storage.

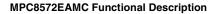

Finally, high-speed Serial RapidIO<sup>™</sup> links are connected from the MPC8572E to AdvancedMC ports 8–11 (and optionally, via resistor links to AdvancedMC ports 4–7). PCI-Express<sup>™</sup> connectivity is available on AdvancedMC ports 4–7 (PCI-Express functionality is mutually exclusive with Serial RapidIO functionality on AdvancedMC ports 4–7).

## 1.2 Working Configuration

There is one configuration for use with the MPC8572EAMC board, which is system development in an AdvancedMC-compatible chassis.

## 1.2.1 System Development Configuration

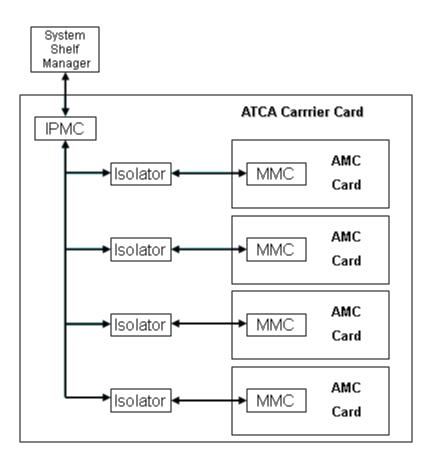

The recommended procedure when configuring the MPC8572EAMC is to run the card using an ATCA, MicroTCA, picoTCA or equivalent chassis. This allows the correct power and air flow to be delivered to

General Information

the board. AdvancedMC boards must be inserted into carrier chassis as directed by the specific carrier's instructions. As in standard development systems, these chassis provide direct connections to JTAG and external connections.

## 1.3 MPC8572EAMC Processor Board

In the following subsystems a detailed description of the board and its connectors is provided.

- Target Use

- System component for media gateway and RNC systems

- Software development platform for media gateway and RNC systems

- System design reference/enablement platform for customers and third parties

- Form Factor

- Single width AdvancedMC size, full height module

- Connectivity

- 2x1000 Base-X Gigabit Ethernet from backplane AdvancedMC ports 0 and 1 to MPC8572E eTSEC3/4 via SGMII PHY

- 2x1000 Base-T Gigabit Ethernet from AdvancedMC front panel (dual RJ-45) to MPC8572E eTSEC1/2 via SGMII PHY

- 1x 10/100 BaseT from AdvancedMC front panel (single RJ-45) directly to MPC8572E FEC via RGMII

- Dual core serial connectivity on AdvancedMC front panel via mini-Type B USB connector (multiplexed)

- x4 Serial RapidIO interfaces on backplane AdvancedMC ports 8–11, connected to MPC8572E SerDes block

- x4 PCI-Express interface on backplane AdvancedMC ports 4–7, connected to MPC8572E SerDes block

- Option to connect x4 Serial RapidIO on backplane AdvancedMC ports 4–7 (at expense of PCI-Express)

- Hardware Blocks

- MPC8572E:

- Two high-performance Power Architecture<sup>™</sup> e500v2 cores with 36-bit physical addressing

- 1024-Kbyte level 2 cache

- Integrated security engine with XOR acceleration

- $-4 \times 1$  GEth enhanced 3-speed Ethernet controllers (SGMII-capable)

- 10/100 Fast Ethernet controller maintenance interface

- 2x DDR2/DDR3 SDRAM memory controllers, one per core

- 3x PCI Express controllers

- 1x Serial RapidIO controller with RapidIO messaging unit

- 2x UART

- Local Bus Controller

- GPIO

- IEEE Std 1149.1<sup>TM</sup> interface

- Board Management

- Hot Swapping

- FRU Storage

- Status LEDs

- Temperature and voltage monitoring

- Power Supply

- 12-V and 3.3-V IPMCV, provided via AdvancedMC edge connector

- On-board voltage requirements are generated via DC-DC voltage regulators:

- 3.3 V for I/O

- 1.1 V for CPU core voltage

- 2.5/1.2 V for Ethernet PHYs

- 1.8/0.9 V for DDR2 SoCDIMMs

- Configuration

- MPC8572E POR configs controlled via user defined DIP switches: SW5, 500, 501

- Additional User switches provided (x4): SW4

- Front panel user reset switch: SW3

- Master reset switch: SW2

- AdvancedMC ports 4–7 selected via soldered resistor links (option A/B)

- MPC8572E Debug

- Chained JTAG header for Reset/System CPLDs

- 16-pin COP header for processor debug

### 1.3.1 External Connectors

The MPC8572EAMC interconnects with external devices via the following set of connectors

- Front Panel, Dual Ethernet Connector (for Eth0/1—GigEth) (P3)

- Front Panel, Single Ethernet Connector (for Eth4—FEC) (P1)

- AdvancedMC Edge Connector (P2)

- USB Mini-Type B connector (J2)

- IEEE Std 1588<sup>TM</sup> Header for Ethernet test (J1)

- USB DUART Connection. Provides debug information from MPC8572E Core #0 /1 (J2).

- MMC BDM Debug header. Reserved for factory use only (J3).

- MPC8572E COP Debug header (J4)

- CPLD JTAG Select. Reserved for factory use only (J6).

- CPLD Programming Header. Reserved for factory use only (HD1).

- MMC Console debug: Pin 1 = TxD, Pin 2 = RxD, Pin 3 = GND (J7)

**General Information**

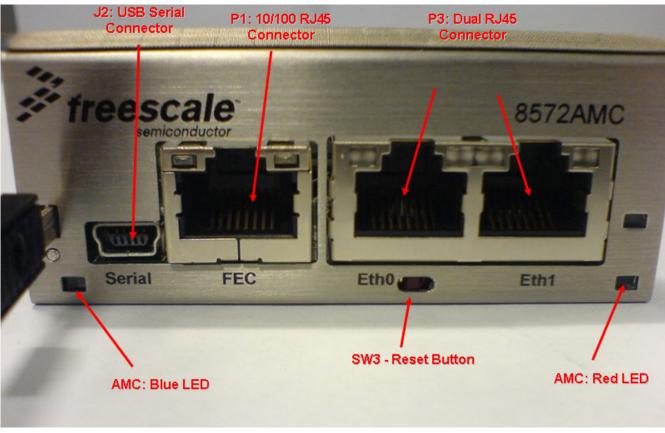

Figure 1-1. MPC8572EAMC Board Front Panel Connections

### NOTE

Users should note that the MPC8572EAMC is shipped with the "U-Boot" bootloader and a Linux Kernel already programmed into the FLASH memory. The Linux kernel uses the ETH0–4 notation, whereas eTSEC1–4 and FEC is the notation used by U-boot.

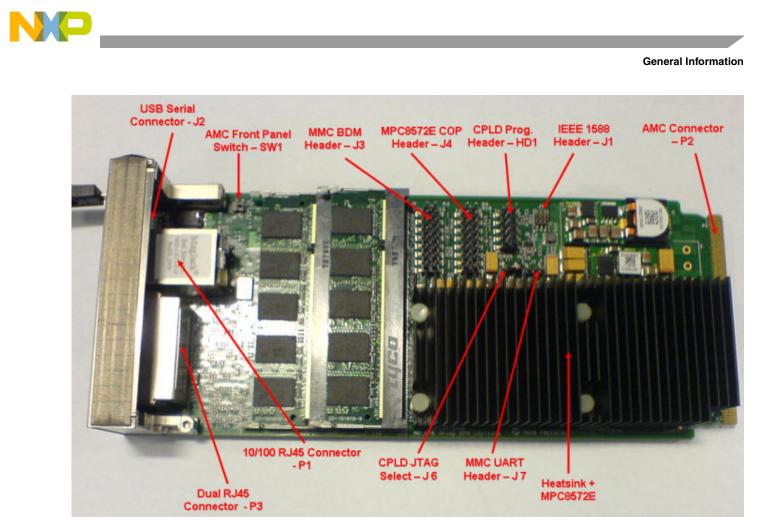

Figure 1-2. MPC8572EAMC Board External Connections

General Information

## 1.4 MPC8572EAMC Block Diagram

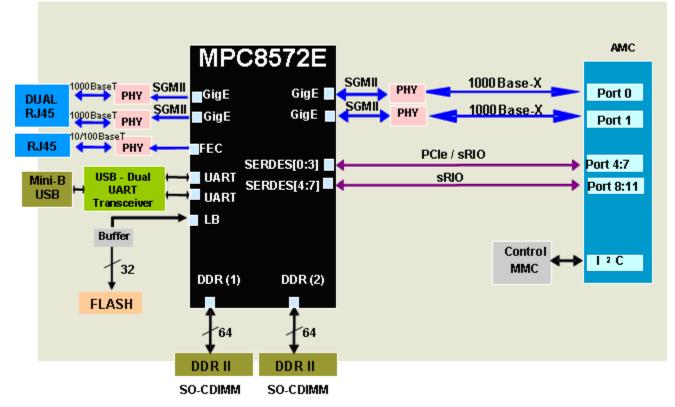

Figure 1-3 shows the block diagram for the MPC8572EAMC.

Figure 1-3. MPC8572EAMC Block Diagram

## 1.5 Definitions, Acronyms, and Abbreviations

Table 1-1 lists definitions, acronyms, and abbreviations.

| Table 1-1. Definitions, | Acronyms, and | Abbreviations |

|-------------------------|---------------|---------------|

|-------------------------|---------------|---------------|

| Acronym    | Definition                                     |

|------------|------------------------------------------------|

| AdvancedMC | Advanced mezzanine card                        |

| ATCA       | Advanced telecommunications computing platform |

| BDM        | Background debugging mode                      |

| CPLD       | Complex programmable logic device              |

| DIP        | Dual in-line package                           |

| DNP        | Do not populate                                |

| DSP        | Digital signal processor                       |

| DUART      | Dual universal asynchronous receive transmit   |

| Acronym   | Definition                                          |

|-----------|-----------------------------------------------------|

| EEPROM    | Electrically erasable programmable read-only memory |

| GETH      | Gigabit Ethernet                                    |

| HW        | Hardware                                            |

| I2C (BUS) | Inter-IC bus                                        |

| MMC       | Module management controller                        |

| POR       | Power-on reset                                      |

| TLA       | Technology license agreement                        |

| UART      | Universal asynchronous receive transmit             |

| μΤϹΑ      | Micro telecommunications computing platform         |

Table 1-1. Definitions, Acronyms, and Abbreviations (continued)

### 1.6 Related Documentation

This document references the following documents:

- *MPC8572EAMC Hardware Getting Started Guide* (MPC8572EAMCGSG)

- *MPC*8572*E PowerQUICC*<sup>™</sup> *III Integrated Host Processor Family Reference Manual* (MPC8572ERM)

- *MPC*8572*E PowerQUICC*<sup>™</sup> *III Integrated Host Processor Hardware Specification* (MPC8572EEC)

- PICMG AMC.0 R2.0, Advanced Mezzanine Base Card Specification

- PICMG AMC.1, R1.0, AdvancedMC PCI Express and AS

- PICMG AMC.2 AdvancedMC Ethernet

- PICMG AMC.4 AdvancedMC Serial RapidIO

### 1.7 Specifications

Table 1-2 lists the specifications for the AdvancedMC board.

| Table 1-2. AdvancedMC | Board Specifications |

|-----------------------|----------------------|

|-----------------------|----------------------|

| Characteristics       | Specifications                                                                        |

|-----------------------|---------------------------------------------------------------------------------------|

| Power requirements    | No external power supply for AdvancedMC modes—powered from ATCA carrier/uTCA chassis. |

| Operating temperature | 0 C to 70 C                                                                           |

| Storage temperature   | -25 C to 85 C                                                                         |

| Characteristics   | Specifications                                                                                                               |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| Relative humidity | 5% to 90% (non condensing)                                                                                                   |

| Dimensions        | Single width AdvancedMC form factor<br>Length = 1806. mm<br>Width = 73.5 mm<br>Height = 17.91 mm<br>Board thickness = 1.6 mm |

#### Table 1-2. AdvancedMC Board Specifications (continued)

Table 1-3 lists the specifications processing support.

#### Table 1-3. Processing Support

| Subsystem           | Component            | Specifications                                                                    |  |

|---------------------|----------------------|-----------------------------------------------------------------------------------|--|

| MPC8572E            | Processor core/speed | Dual cores running up to 1.5 GHz                                                  |  |

| Memory              | EEPROM               | x32 128-Mbyte                                                                     |  |

|                     | DDRII                | 2 Gbytes, 32-bit wide DDR2 (up to 800 MHz) (2 $\times$ 1 Gbyte SoCDIMMS)          |  |

| Communication ports | Gigabit Ethernet     | SGMII GigE SERDES from MPC8572E to front and back panels.                         |  |

|                     | Fast Ethernet        | RGMII 10/100 Ethernet from MPC8572E to front panel.                               |  |

|                     | Serial RapidIO       | x1/x4 Serial RapidIO<br>Switch configurable for 1.25/2.5 or 3.125 Gbps data rate  |  |

|                     | PCI-Express          | x4 capability on AdvancedMC ports 4–7 (Option A resistor configuration) 2.5 Gbps. |  |

|                     | UART                 | RS232-USB transceiver allows data exchange from both cores.                       |  |

## Chapter 2 Hardware Preparation and Installation

This chapter details the unpacking instructions, hardware preparation and installation instructions for the MPC8572EAMC processor board. For details on hardware preparation, please refer to the *MPC8572EAMC Hardware Getting Started Guide* (MPC8572EAMCGSG).

## 2.1 Unpacking Instructions

### NOTE

Upon receipt, if the shipping carton is damaged, request the carrier agent be present during the unpacking and inspection of the equipment.

### CAUTION

Avoid touching areas of integrated circuitry as static discharge can damage board devices.

- Unpack equipment from shipping carton

- Refer to packing list and verify that all items are present

- Save packing material for storing and reshipping of equipment

## 2.2 Installation Instructions

Perform the following steps in the order listed to install the MPC8572EAMC Processor Board properly.

- 1. Verify that jumpers and switches are in their default positions (See Chapter 4, "Controls and Indicators," for a list of default positions).

- 2. Connect external cables in accordance with your needs (See Section 1.3.1, "External Connectors," for more details).

- 3. Insert the board into the carrier/chassis as per the specific chassis operating instructions.

- 4. Switch on the power to the chassis.

- 5. Check for completion of the reset sequence indicated by the LEDs; see Figure 4-1 for locations. A full description of the LEDs is given in Table 4-3.

- 6. Check for the blue front panel LED and power good LEDs being illuminated. (A full description of the LED operation is given in Section 4.3, "LEDs"). This indicates the board power is applied.

- 7. Insert the AdvancedMC front panel handle and check that the blue LED blinks twice then goes out. Then check for completion of the reset sequence by verifying the following LEDs:

- The "System Status" LED, LD507, switches on, then goes off once system configuration is complete. LD506 should stay on indicating the processor is "Ready."

Hardware Preparation and Installation

- 8. Ethernet backplane port activity LEDs D501, D502 (for ETH2/eTSEC2-AMC Port 0) and LEDs D504, D505 (for ETH3/eTSEC3-AMC Port 1) are illuminated if there is a physical network link on Port 0 or 1 of the AdvancedMC backplane.

- 9. Ethernet front panel activity is indicated on the front panel LEDs of the respective RJ-45 PHY connections.

- 10. USB UART activity is shown on LEDS D507 and D508. A USB cable must be connected between the host PC and the front panel USB connector. A serial terminal can be set up using a PC communication program, such as HyperTerminal, set to 115200-8-N-1 baud rate. If the USB session disconnects (for example, when power is cycled), then the communication link must be disconnected and reconnected again.

- 11. Pressing the front panel reset button SW3 resets the board and starts the reset sequence.

- 12. Pressing the reset button SW2 power-cycles the board and starts the reset sequence.

- 13. Operate the CodeWarrior IDE software to verify that the board is installed properly

## Chapter 3 Memory Map

The MPC8572EAMC is shipped with the following memory map as described in Table 3-1.

| Base Address | Device                    | Size       |

|--------------|---------------------------|------------|

| 0x0000_0000  | DDR Controller 1 (64-bit) | 1 Gbyte    |

| 0x4000_0000  | DDR Controller 2 (64-bit) | 1 Gbyte    |

| 0x8000_0000  | PCI Express Memory        | 1 Gbyte    |

| 0xC000_0000  | Serial RapidIO Controller | 512 Mbytes |

| 0xF800_0000  | Local Bus FLASH           | 128 Mbytes |

| 0xFFC0_0000  | PCI-Express I/O           | 64 Kbytes  |

| 0xFFE0_0000  | CCSR                      | 1 Mbyte    |

#### Table 3-1. MPC8572EAMC Memory Map

Memory Map

## Chapter 4 Controls and Indicators

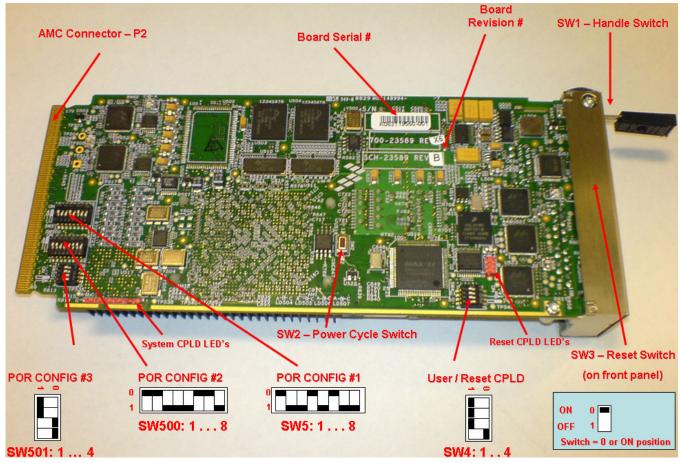

This chapter describes the controls and indicators for the MPC8572EAMC processor board, which includes switches, jumpers, LEDs, and push button switches, shown in Figure 4-1.

Figure 4-1. MPC8572EAMC—Switches, Jumpers, LEDs and Push Buttons

Controls and Indicators

## 4.1 DIP Switch Settings

Figure 4-1 shows the location of the DIP switches on the board and their default (factory) position. Table 4-1 describes the possible settings of all DIP switches on the boards. Note that when in the "ON" position, the value of the switch is zero. For a detailed description of the bits and fields, refer to the Section 4.4.3, "Power-On Reset Configuration" in the *MPC8572E PowerQUICC*<sup>TM</sup> *III Integrated Host Processor Family Reference Manual, Revision 2.*

| Feature | Default Settings<br>[OFF = 1, ON = 0)                                                                                                                                           | Comments                                                                                                                                                                                                                                                                                                   |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | SW4                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |  |

| SW4.1   | OFF                                                                                                                                                                             | Reserved                                                                                                                                                                                                                                                                                                   |  |

| SW4.2   | OFF                                                                                                                                                                             | Reserved                                                                                                                                                                                                                                                                                                   |  |

| SW4.3   | OFF                                                                                                                                                                             | Reserved                                                                                                                                                                                                                                                                                                   |  |

| SW4.4   | ON                                                                                                                                                                              | [SW4.4] = MMC H/W Select. ON—MMC present <sup>1</sup><br>[SW4.4] = MMC H/W Select. OFF—MMC not present                                                                                                                                                                                                     |  |

|         |                                                                                                                                                                                 | SW5                                                                                                                                                                                                                                                                                                        |  |

| SW5.1   | ON                                                                                                                                                                              | [SW5.1:2] = ON:ON. CCB:SYSCLK = 4:1 (266 MHz)                                                                                                                                                                                                                                                              |  |

| SW5.2   | OFF                                                                                                                                                                             | [SW5.1:2] = OFF:ON. CCB:SYSCLK = 8:1 (533 MHz)<br>[SW5.1:2] = ON:OFF. CCB:SYSCLK = 10:1 (666 MHz) <sup>1</sup><br>[SW5.1:2] = OFF:OFF. CCB:SYSCLK = 12:1 (800 MHz)                                                                                                                                         |  |

| SW5.3   | OFF                                                                                                                                                                             | [SW5.3:4] = ON:ON. e500 Core #0:CCB = 1.5:1                                                                                                                                                                                                                                                                |  |

| SW5.4   | ON                                                                                                                                                                              | [SW5.3:4] = OFF:ON. e500 Core #0:CCB = 2:1 <sup>1</sup><br>[SW5.3:4] = ON:OFF. e500 Core #0:CCB = 2.5:1<br>[SW5.3:4] = OFF:OFF. e500 Core #0:CCB = 3.5:                                                                                                                                                    |  |

| SW5.5   | OFF                                                                                                                                                                             | [SW5.5:6] = ON:ON. e500 Core #1:CCB = 1.5:1                                                                                                                                                                                                                                                                |  |

| SW5.6   | 6         ON         [SW5.5:6] = OFF:ON. e500 Core #1:CCB = 2:1 <sup>1</sup> [SW5.5:6] = ON:OFF. e500 Core #1:CCB = 2.5:1         [SW5.5:6] = OFF:OFF. e500 Core #1:CCB = 3.5:1 |                                                                                                                                                                                                                                                                                                            |  |

| SW5.7   | OFF                                                                                                                                                                             | [SW5.7:8] = ON:ON. Boot ROM Location = PCI-Express                                                                                                                                                                                                                                                         |  |

| SW5.8   | OFF                                                                                                                                                                             | [SW5.7:8] = OFF:ON. Boot ROM Location = Serial RapidIO<br>[SW5.7:8] = ON:OFF. Boot ROM Location = DDR Memory<br>[SW5.7:8] = OFF:OFF. Boot ROM Location = 32-bit Local FLASH Memory <sup>1</sup>                                                                                                            |  |

|         | SW500                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |  |

| SW500.1 | ON                                                                                                                                                                              | [SW500.1:3]=ON:ON.DDR Clock Ratio = 3:1 DDRCLK (200 MHz)                                                                                                                                                                                                                                                   |  |

| SW500.2 | ON                                                                                                                                                                              | [SW500.1:3]=OFF:ON:ON.DDR Clock Ratio = 4:1 DDRCLK (266 MHz)<br>[SW500.1:3]=ON:OFF:ON.DDR Clock Ratio = 6:1 DDRCLK (400 MHz)                                                                                                                                                                               |  |

| SW500.3 | OFF                                                                                                                                                                             | [SW500.1:3]=OFF:OFF:ON.DDR Clock Ratio = 8:1 DDRCLK (533 MHz)<br>[SW500.1:3]=ON:ON:OFF.DDR Clock Ratio = 10:1 DDRCLK (666 MHz) <sup>1</sup><br>[SW500.1:3]=OFF:ON:OFF.DDR Clock Ratio = 12:1 DDRCLK (800 MHz)<br>[SW500.1:3]=ON:OFF:OFF. RESERVED<br>[SW500.1:3]=OFF:OFF:OFF.DDR Clock Ratio = SYNCHRONOUS |  |

| Feature | Default Settings<br>[OFF = 1, ON = 0) |                                                                                                                                                                                                                                                                                             |  |

|---------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SW500.4 | OFF                                   | [SW500.4:5] = ON:ON. MPC8572E acts as agent on all interfaces                                                                                                                                                                                                                               |  |

| SW500.5 | OFF                                   | [SW500.4:5] = OFF:ON. MPC8572E acts as end point on PCIE #1 host<br>[SW500.4:5] = ON:OFF. MPC8572E acts as end point on SRIO & PCIE #1 host<br>[SW500.4:5] = OFF:OFF. MPC8572E acts as the host processor <sup>1</sup>                                                                      |  |

| SW500.6 | ON                                    | [SW500.6:8] = OFF:ON:ON. IO Port Selection = SRIO 100-MHz clock, 2.5 Gbps (x4)                                                                                                                                                                                                              |  |

| SW500.7 | ON                                    | [SW500.6:8] = ON:OFF:ON. IO Port Selection = SRIO/PCIE 100-MHz clock, 2.5 Gbps<br>[SW500.6:8] = OFF:OFF:ON. IO Port Selection = SRIO/PCIE 100-MHz clock, 1.25/2.5 Gbps (x4)                                                                                                                 |  |

| SW500.8 | OFF                                   | [SW500.6:8] = OFF:ON:OFF. IO Port Selection = SRIO 100-MHz clock, 1.25 Gbps (x4)<br>[SW500.6:8] = ON:ON:OFF. IO Port Selection = SRIO 125 MHz, 3.125 Gbps (x4) <sup>1</sup>                                                                                                                 |  |

|         | SW501                                 |                                                                                                                                                                                                                                                                                             |  |

| SW501.1 | OFF                                   | [SW501.1] = ON Boot Sequence Configuration = Boot Sequencer Enabled<br>[SW501.1] = OFF Boot Sequence Configuration = Boot Sequencer Disabled <sup>1</sup>                                                                                                                                   |  |

| SW501.2 | OFF                                   | CPU Boot Config:                                                                                                                                                                                                                                                                            |  |

| SW501.3 | ON                                    | [SW501.2:3] = ON:ON.CPU boot hold-off both cores<br>[SW501.2:3] = OFF:ON. E500 Core 0 allowed to boot, Core 1 in boot hold-off <sup>1</sup><br>[SW501.2:3] = ON:OFF. E500 Core 1 allowed to boot, Core 0 in boot hold-off<br>[SW501.2:3] = OFF:OFF. Both cores boot without external master |  |

| SW501.4 | ON                                    | RIO System Size:<br>[SW501.4] = ON. Large system size, up to 65,536 devices <sup>1</sup><br>[SW501.4] = OFF. Small system size, up to 256 devices                                                                                                                                           |  |

#### Table 4-1. MPC8572EAMC DIP Switch Listing (continued)

Note:

<sup>1</sup> Default

Check the default positions of the board first and ensure that the board is operational before changing any settings. Please also ensure that the selected settings are within the maximum supported operating characteristics of the device.

### 4.2 Jumpers

There is one jumper on the board as described in Table 4-2. This jumper is used to include or isolate the System CPLD from the JTAG chain.

**Table 4-2. Jumper Position**

| Jumper | Description                                                                                                                                                                                   |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J12    | <ul> <li>Selects the Reset and System CPLD JTAG chain.</li> <li>Position 1-2: only Reset CPLD is in the chain</li> <li>Position 2-3: both Reset and System CPLDs are in the chain.</li> </ul> |

Note: If the Reset CPLD is blank, then position 1-2 must be used to program it.

Controls and Indicators

## 4.3 LEDs

Table 4-3 describes the functions of the LEDs on the MPC8572EAMC Processor Board. The physical locations of the LEDs are shown in Figure 4-1.

| Description                                  | Ref      | Color            | LED On                                   | LED Off                           |

|----------------------------------------------|----------|------------------|------------------------------------------|-----------------------------------|

| MMC red LED                                  | LD1      | Red              | MMC control                              | Normal operation                  |

| MMC card power blue LED                      | LD500    | Blue             | Hot swap state                           | Hot swap state                    |

| Port 0 AMC SERDES Ethernet Rx activity       | D500     | Green            | Rx Ethernet activity                     | No Rx Ethernet activity           |

| Port 0 AMC SERDES Ethernet Tx activity       | D501     | Yellow           | Tx Ethernet activity                     | No Tx Ethernet activity           |

| Port 0 AMC SERDES LOS                        | D502     | Orange           | Loss of signal                           | No loss of signal                 |

| Port 1 AMC SERDES LOS                        | D504     | Orange           | Loss of signal                           | No loss of signal                 |

| Port 1 AMC SERDES Ethernet Tx activity       | D505     | Yellow           | Tx Ethernet activity                     | No Tx Ethernet activity           |

| Port 1 AMC SERDES Ethernet Rx activity       | D506     | Green            | Rx Ethernet activity                     | No Rx Ethernet activity           |

| USB/UART 1 activity                          | D507     | Orange           | UART 1 activity                          | No UART 1 activity                |

| USB/UART 0 activity                          | D508     | Orange           | UART 0 activity                          | No UART 0 activity                |

| Front panel dual RJ45 Ethernet Rx activity   | P3:D1-2a | Green            | Rx Ethernet activity                     | No Rx Ethernet activity           |

| Front panel dual RJ45 Ethernet Tx activity   | P3:D1-4a | Yellow           | Tx Ethernet activity                     | No Tx Ethernet activity           |

| Front panel dual RJ45 Ethernet Rx activity   | P3:D1-2b | Green            | Rx Ethernet activity                     | No Rx Ethernet activity           |

| Front panel dual RJ45 Ethernet Tx activity   | P3:D1-4b | Yellow           | Tx Ethernet activity                     | No Tx Ethernet activity           |

| Front panel 10/100 RJ45 Ethernet Rx activity | P1       | Orange/<br>Green | Rx Ethernet activity                     | No Rx Ethernet activity           |

| Front panel 10/100 RJ45 Ethernet Tx activity | P1       | Yellow           | Tx Ethernet activity                     | No Tx Ethernet activity           |

| General debug System CPLD                    | LD507    | Green            | System CPLD<br>execution not<br>complete | System CPLD execution complete    |

| General debug System CPLD                    | LD506    | Green            | Ready signal                             | POR config cycles<br>unsuccessful |

| General debug System CPLD                    | LD505    | Yellow           | Default on                               | User debug #1                     |

| General debug System CPLD                    | LD504    | Yellow           | Default on                               | User debug #2                     |

| General debug POR CPLD                       | LD502    | Green            | User config #1                           | User config #1                    |

| General debug POR CPLD                       | LD501    | Yellow           | User config #2                           | User config #2                    |

| General debug POR CPLD                       | LD503    | Yellow           | User config #3                           | User config #3                    |

#### Table 4-3. LED Description

### 4.4 Headers

The MPC8572EAMC Processor Board has a number of headers used to connect a serial terminal to the module management controller. An additional IEEE 1588 test interface header is also provided. These are detailed in Table 4-4.

| Header | Description                                                                                                                                                                                                                                                                                                   |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| J2     | MMC serial interface header<br>• Pin1: Serial transmit data output (TxD)<br>• Pin2: Serial transmit data output (RxD)<br>• Pin3: Digital ground (GND)                                                                                                                                                         |  |  |

| J10    | IEEE 1588 test interface header<br>• Pin1: IEEE 1588 trigger output (trig_out)<br>• Pin2: IEEE 1588 trigger input (trig_in)<br>• Pin3: IEEE 1588 trigger output (pulse_out1)<br>• Pin4: IEEE 1588 trigger output (pulse_out2)<br>• Pin5: IEEE 1588 clock output (clk_out)<br>• Pin6: Spare pull-down resistor |  |  |

### 4.5 Push Buttons

Figure 4-2 describes the MPC8572EAMC Processor Board push buttons.

| SW3<br>Board Reset | Pressing button SW3 on the<br>front panel causes an<br>HRESET to the MPC8572E                  |

|--------------------|------------------------------------------------------------------------------------------------|

| SW2<br>Power Cycle | Pressing button SW2 on the<br>rear center section of the<br>board recycles the boards<br>power |

Figure 4-2. MPC8572EAMC Push Button Switches

**Controls and Indicators**

## Chapter 5 MPC8572EAMC Functional Description

This chapter describes the design details of the various MPC8572EAMC hardware blocks. The hardware description has been partitioned into the following logical sections:

- MPC8572E Microprocessor Block

- MPC8572EAMC Ethernet Connectivity

- MPC8572EAMC System Clocking

- MPC8572EAMC Board Control (Power, Reset, Logic)

- AdvancedMC Backplane Connector

- Module Management Controller (MMC)

- Thermal Requirements

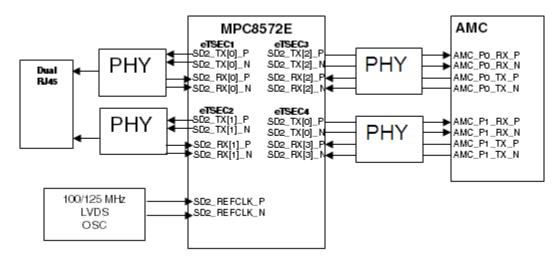

The MPC8572EAMC with AMC.1 (PCI Express (and PCI Express Advanced Switching)), AMC.2 (Gigabit Ethernet and XAUI) and AMC.4 (Serial RapidIO interface), fitting into a single-width, full height AdvancedMC. The card contains a single MPC8572E Dual core processor with dual DDR2 memory SoCDIMMs. The MPC8572E has four (SGMII) capable Gigabit Ethernet interfaces, two of which are connected to the backplane via two SGMII PHYs. The other two Gigabit Ethernet interfaces are connected to the front panel onto a dual RJ-45 connector, via two further SGMII PHYs. A further 10/100 Fast Ethernet interface is supported by the MPC8572E and this is connected to the front panel via a RGMII PHY. Serial RapidIO and PCI-Express connectivity to the AdvancedMC backplane is made using high speed SERDES links. Serial (debug) communication with the MPC8572E is made using a mini-type B USB front panel socket that connects to a dual UART-USB transceiver chip. On the local bus of the MPC8572E is located a 128-Mbyte FLASH memory, which is used to store the operating and file systems for the MPC8572EAMC. This FLASH can be programmed directly using debugging tools, such as CodeWarrior, through the MPC8572E microprocessor.

### 5.1 MPC8572E Microprocessor Block

The MPC8572E microprocessor block consists of a dual core, e500 MPC8572E, dual DDR2/3 memory controllers and associated interfaces.

### 5.1.1 MPC8572E DDR Memory

The MPC8572E microprocessor provides two 64-bit data DDRII/III interfaces (with 8-bit ECC) up to a maximum data rate of 800 MHz (each core has its own dedicated DDR memory interface). On the MPC8572EAMC there are two Vertium SoCDIMM DIMMs. The VL491T2863T is a 128-Mbit × 72

#### MPC8572EAMC Functional Description

DDR2 SDRAM high density SO-CDIMM. Control of each memory DIMM is via the MPC8572E's DDR controllers chip select (CS) signals, shown in Table 5-1.

| Pin Name  | CS Resources | Address    | Comments                                |

|-----------|--------------|------------|-----------------------------------------|

| D1_MCS0   | DDR SDRAM    | 0x00000000 | 64-bit, controlled by DDR controller #1 |

| D1_MCS1   | DDR SDRAM    | 0x00000000 | 64-bit, controlled by DDR controller #1 |

| D1_MCS2-3 | Unused       | Unused     | Unused                                  |

| D2_MCS0   | DDR SDRAM    | 0x40000000 | 64-bit, controlled by DDR controller #2 |

| D2_MCS1   | DDR SDRAM    | 0x40000000 | 64-bit, controlled by DDR controller #2 |

| D2_MCS2-3 | Unused       | Unused     | Unused                                  |

Table 5-1. MPC8572E DDR Chip Select Resources and Memory map

Figure 5-1 illustrates how the DDR controller interfaces on the MPC8572E device and provides a glueless connection to the two 128-Mbit  $\times$  72 SoCDIMMs on the MPC8572EAMC.

|           | D1_MA[15:0]                      |          |

|-----------|----------------------------------|----------|

| DDRII     | D1 MRAS/MCAS/MWE                 | MPC8572E |

|           | D1_MBA[2:0]                      |          |

| SOCDIMM   | D1 MDQ[15:0]                     |          |

| 000011111 | D1_MDQS/#DQS[8:0]<br>D1_MDM[8:0] |          |

| 128Mx72   | D1 MECC[7:0]                     |          |

|           | D1 MCS/MCKE/MODT[1:0]            |          |

|           | D1 MCLK/#CLK[5:0]                |          |

|           |                                  |          |

|           |                                  |          |

|           | D2_MA[15:0]                      |          |

|           | D2_MRAS/MCAS/MWE                 |          |

| DDRII     | D2_MBA[2:0]                      |          |

|           | D2 MDQ[15:0]                     |          |

| SOCDIMM   | D2_MDQS/#DQS[8:0]                |          |

|           | D2_MDM[8:0]                      |          |

| 128Mx72   | D2_MECC[7:0]                     |          |

|           | D2_MCS7MCKE7MODT[1:0]            |          |

|           | D2_MCLK/#CLK[5:0]                |          |

| 1         | 1                                |          |

Figure 5-1. DDR2 Connectivity

### 5.1.1.1 DDR Groups

Every DDR2 signal can be considered to be a member of one of four separate DDR signal groups. Each group has a unique set of rules in terms of their connection and routing on the AdvancedMC board. These four groups are shown in Table 5-2.

| Signal Group        | Signal      | Description              | I/O (w.r.t.<br>Processor) |

|---------------------|-------------|--------------------------|---------------------------|

| Address and command | MA[0:15]    | Address bus              | 0                         |

|                     | MBA[0:2]    | Bank address bus         | 0                         |

|                     | #MWE        | Write enable             | 0                         |

|                     | #MCAS       | Column address strobe    | 0                         |

|                     | #MRAS       | Row address strobe       | 0                         |

| Control             | MCKE[0:3]   | Clock enable             | 0                         |

|                     | #MCS[0:3]   | Chip select              | 0                         |

|                     | MODT[0:3]   | On-die termination       | 0                         |

|                     | MDIC[0:1]   | DDR internal calibration | I                         |

| Data                | MDQS[0:8]   | Data strobes             | I/O                       |

|                     | #MDQS[0:8]A | Data strobes complement  | I/O                       |

|                     | MDM[0:8]    | Data mask                | 0                         |

|                     | MDQ[0:63]   | Data bus                 | I/O                       |

|                     | MECC[0:7]   | Error correction bits    | I/O                       |

| Clocks              | MCK[0:5]    | Clock                    | 0                         |

|                     | #MCK[0:5]   | Clocks complement        | 0                         |

Table 5-2. DDR2 Interface Signals

Complex DDR2 timing adaptation is available via the DDR clocking subsystem of the MPC8572E. It supports the following:

- Sampling of the input data from the DDR2 memory

- Positioning of the DQS output signals during writes to the DDR2 memory

- Synchronizing the incoming DDR2 data to the internal clock

- Control the relationship between output data and CLK\_OUT

### 5.1.1.2 Terminations and I/O Voltage

The DDR2 interface operates at 1.8 V I/O voltages. Reference voltages of 0.9 V are synthesized from a 5-V supply via the TPS51116 voltage regulator. This reference voltage is applied to each DDR2 device (at the VREF pin) and the MPC8572E (at pin MVREF).

The DDR2 interface on the MPC8572E has the addition of the On-Die Termination (ODT) signals. ODT signals are used to control the termination of the data group signals in the DDRII DRAM device. DDR2

#### MPC8572EAMC Functional Description

uses a termination scheme where the signals terminated in the DRAM device and the controller by internal termination resistors, such as ODT. A compensation capacitor is also not required for the control signals on the board.

### 5.1.2 Serial RapidIO Interface

The RapidIO controller supports a high-performance, point-to-point, low pin count packet, switched-level interconnect that can be used in a variety of applications as an open standard. The MPC8572E serial RapidIO subsystem complies with the RapidIO Interconnect Specification Revision 1.2, which connects directly to the AdvancedMC backplane. Serial RapidIO is statically connected to AdvancedMC ports 8–11 on the backplane and optionally on AdvancedMC ports 4–7 (which it shares with PCI-Express).

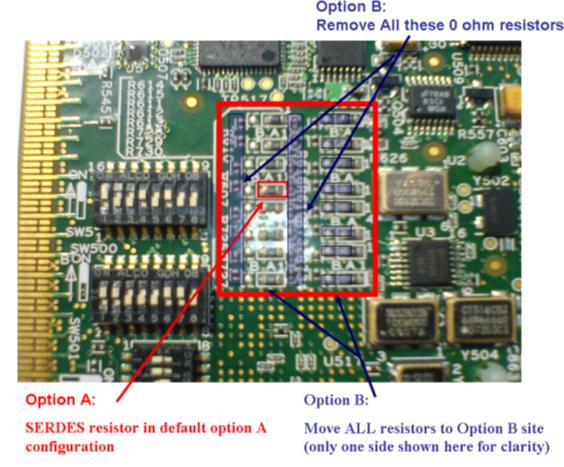

Using serial RapidIO on AdvancedMC ports 4–7 involves desoldering configuration resistors R729, R730, R625, R735, R611, R612, R623, R624, R613, R728, R736, R737, R614, R615, R621 and R622, from the default Option A position (PCI-Express on AdvancedMC ports 4–7) to Option B position (serial RapidIO on AdvancedMC ports 4–7). Figure 5-2 shows the position of these resistors on the MPC8572EAMC board.

The interface can work in x1 or x4 mode and is selectable via user DIP switches during the POR configuration phase. Table 5-3 illustrates the possible peripheral combinations that are possible on the MPC8572EAMC's fabric port region.

| MPC8572EAMC Port # | Option A       | Option B |

|--------------------|----------------|----------|

| 4                  | PCI-Express x4 | SRIO x4  |

| 5                  |                |          |

| 6                  |                |          |

| 7                  |                |          |

| 8                  | SRIO x4        | SRIO x4  |

| 9                  |                |          |

| 10                 |                |          |

| 11                 |                |          |

Table 5-3. Serial RapidIO/PCI-Express Board Options

#### MPC8572EAMC Functional Description

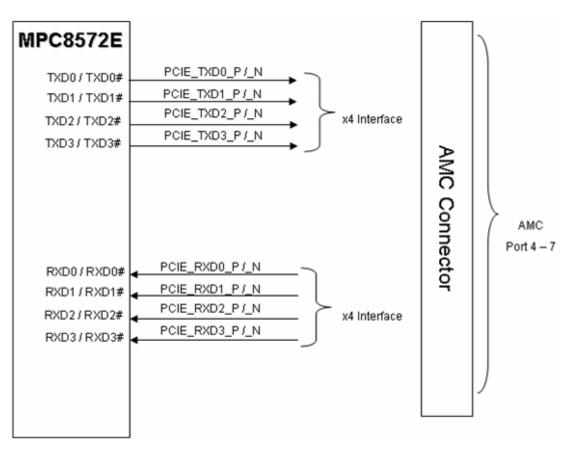

Figure 5-3 illustrates how the SRIO interface signals are connected to the MPC8572E microprocessor and the AdvancedMC edge connector, and how they relate to the SERDES resistor options.

| MPC8572E<br>TXD0 / TXD0#<br>TXD1 / TXD1#<br>TXD2 / TXD2#<br>TXD3 / TXD3#<br>RXD0 / RXD0#<br>RXD1 / RXD1#<br>RXD1 / RXD1#<br>RXD2 / RXD2#<br>RXD3 / RXD3# | PCIE_TXD0_P /_N<br>PCIE_TXD1_P /_N<br>PCIE_TXD2_P /_N<br>PCIE_TXD3_P /_N<br>PCIE_RXD0_P /_N<br>PCIE_RXD0_P /_N<br>PCIE_RXD1_P /_N<br>PCIE_R | AMC C         | AMC<br>Port 4 - 7  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|

| TXD8 / TXD8#<br>TXD9 / TXD9#<br>TXD10 / TXD10#<br>TXD11 / TXD11#                                                                                         | SRIO_SD1_TX0_P/_N<br>SRIO_SD1_TX1_P/_N<br>SRIO_SD1_TX2_P/_N<br>SRIO_SD1_TX3_P/_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AMC Connector |                    |

| RXD8 / RXD8#<br>RXD9 / RXD9#<br>RXD10 / RXD10#<br>RXD11 / RXD11#                                                                                         | SRI0_SD1_RX1_P/_N<br>SRI0_SD1_RX2_P/_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | AMC<br>Port 8 - 11 |

#### Figure 5-3. Serial RapidIO Connectivity

#### NOTE

In order for serial RapidIO to co-exist with PCI-Express functionality on the MPC8572EAMC, two SERDES clock rates must be supported: 100 MHz for PCI-Express and 1.25/2.5 Gbps Serial RapidIO, and 125 MHz for 3.125 Gbps Serial RapidIO. Depending on the POR configuration setting for IO configuration bits, this clock frequency is automatically selected by the System CPLD logic.

### 5.1.3 PCI-Express Interface

The MPC8572E PCI Express interface complies with the *PCI Express™ Base Specification, Revision 1.0a* (available from http://www.pcisig.org). The PCI Express controller connects the internal platform to a 2.5-GHz serial interface. As both an initiator and a target device, the PCI Express interface is capable of high-bandwidth data transfer and is designed to support next generation I/O devices. The PCI Express controller can be configured to operate as either a PCI Express root complex (RC) or an endpoint (EP)

device. An RC device connects the host CPU/memory subsystem to I/O devices while an EP device typically denotes a peripheral or I/O device.

Due to pin multiplexing on the MPC8572E device and the available ports on the AdvancedMC connector, PCI-Express x8 mode does not allow simultaneous use of the Serial RapidIO connection. This is caused by the fact that in x8 mode, PCI-Express uses Port 8–11 onto which the Serial RapidIO is connected. Therefore, x8 PCI-Express is not a supported option. See Table 5-2 for the allowed PCI-Express/Serial RapidIO connections. Figure 5-4 illustrates how the PCI-Express is connected to the MPC8572E microprocessor and the AdvancedMC edge connector.

Figure 5-4. PCI-Express Connectivity

MPC8572EAMC Functional Description

### 5.1.4 Local Bus Interface

The MPC8572E enhanced local bus controller (eLBC) supports three interface types, general purpose chip select machine (GPCM), NAND Flash control machine (FCM) and user programmable machines (UPMs). The LBC memory controller supports up to 8 banks of memory selected via separate different Chip Select signals, these are shown in Table 5-4.

Table 5-4. MPC8572E Local Bus Chip Select Resources and Memory Map

| Pin Name | CS Resources | Address    | Comments                                                  |

|----------|--------------|------------|-----------------------------------------------------------|

| LCS0     | Boot Flash   | 0xF8000000 | 32-bit NOR 128-Mbit Flash controlled by GPCM on local bus |

| LCS1-7   | Unused       | Unused     | Unused                                                    |

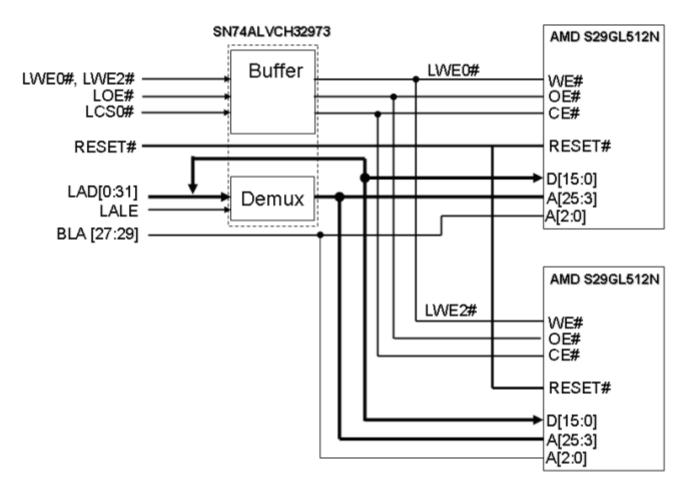

On the MPC8572EAMC, the MPC8572E's 32-bit local bus is used to connect to 128 Mbytes of FLASH memory. This is physically implemented using two AMD S29GL512N Flash devices. In order to minimize the pin count on the MPC8572E device, both the address and data pins are multiplexed. Two SN74ALVCH32973 devices are used on the MPC8572EAMC to both buffer and de-multiplex the MPC8572E local address/data bus signals onto a dedicated address bus and dedicated 32-bit data bus.

Figure 5-5 illustrates how the FLASH ROM is connected to the local bus on the MPC572EAMC.

Figure 5-5. Local Bus FLASH ROM Configuration

#### 5.1.4.1 MPC8572E Interrupts

The MPC8572E has a programmable interrupt controller (PIC) unit that prioritizes and manages interrupts from on chip peripherals as well as interrupt signals from three sources: external to the integrated device, internal to the integrated device, and intrinsic to the PIC itself. The PIC has twelve interrupt request lines INT[0–11]. The polarity and sense of each of these signals is programmable, with each being capable of being driven completely asynchronously. Table 5-5 details the interrupt usage on the MPC8572EAMC board.

| Name Interrupt Sourc |              |

|----------------------|--------------|

| INT0-2               | Unused       |

| INT3                 | Eth 0–4 PHYs |

| INT4                 | System CPLD  |

MPC8572EAMC Functional Description

| Name Interrupt Source |             |

|-----------------------|-------------|

| INT5                  | System CPLD |

| INT6-11               | Unused      |

Table 5-5. MPC8572E Interrupt Assignment (continued)

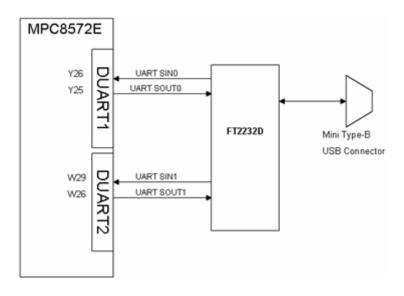

### 5.1.5 MPC8572E DUART1/2

The MPC8572E's DUART1/2 controller is used in conjunction with a FT2232D dual USB UART transceiver to implement two UART interfaces to one USB connector. External serial connection to the front panel of the card is made through a Mini-Type B USB connector. Figure 5-6 shows how the UART-USB serial connection is implemented on this design. (The #DEVID signal on the Mini-Type B USB connector is connected to a test point for debug purposes).

Figure 5-6. DUART Connectivity

#### NOTE

The USB/UART circuitry uses +5 V power generated within the MPC8572EAMC, and not that taken from the external +5 V device/supply.

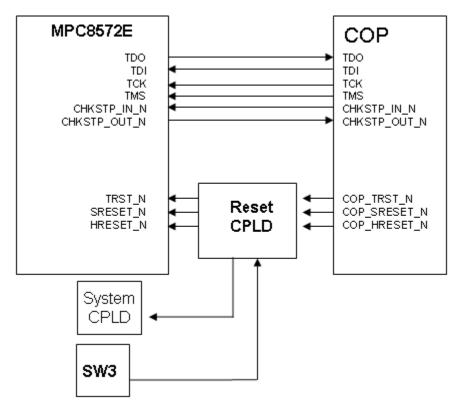

### 5.1.6 COP/JTAG Debug Interface

In order to facilitate system testing, the MPC8572E provides a JTAG test access port (TAP) that complies with the IEEE 1149.1 boundary-scan specification. The common on-chip processor (COP) is part of the MPC8572E's JTAG machine and is implemented as an additional set of instructions/logic. The 16-pin JTAG port allows third party debug tools to be connected to the MPC8572E to allow extensive system debug. Table 5-6 shows the different signals on the COP/JTAG interface.

| Pin | Signal       | Description                                                                            |

|-----|--------------|----------------------------------------------------------------------------------------|

| 1   | TDO          | Transmit Data Out—MPC8572E's JTAG serial data output pin                               |

| 2   | NC           | No Connect                                                                             |

| 3   | TDI          | Transmit Data in—MPC8572E's JTAG serial data input pin                                 |

| 4   | TRST#        | Test Port Reset. Used to reset the JTAG logic on the MPC8572E                          |

| 5   | +3.3 V       | +3.3 V Power                                                                           |

| 6   | +3.3 V       | +3.3 V Power                                                                           |

| 7   | TCLK         | Test Port Clock. This clock is used to shift data in/out of the MPC8572E's JTAG logic. |

| 8   | CHK_STP_IN#  | Check Stop In. This pin is pulled up to 3.3 V via a 10 k resistor.                     |

| 9   | TMS          | Test Mode Select. This pin is used to change the state of the JTAG machine             |

| 10  | NC           | No Connect                                                                             |

| 11  | SRESET#      | Soft Reset. The MPC8572E's soft reset signal                                           |

| 12  | NC           | No Connect                                                                             |

| 13  | HRESET#      | Hard Reset. The MPC8572E's hard reset signal                                           |

| 14  | NC           | No Connect                                                                             |

| 15  | CHK_STP_OUT# | Check Stop Out. This pin is pulled up to 3.3 V via a 10 k resistor.                    |

| 16  | GND          | Digital ground                                                                         |

#### MPC8572EAMC Functional Description

The MPC8572E's COP/JTAG interface can be accessed via a dedicated 16-pin header on the card itself. Figure 5-7 illustrates the connection between the AdvancedMC connector, Reset CPLD, 16-pin JTAG header, and the MPC8572E.

Figure 5-7. COP/JTAG Connectivity MPC8572EAMC

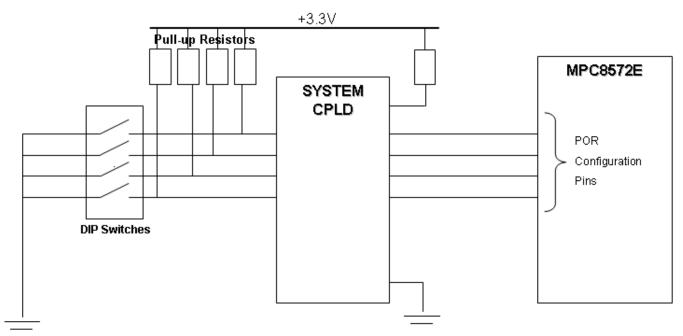

# 5.1.7 MPC8572E Power-On Reset Configuration (POR Config)

The power-on reset configuration of the PowerQUICC<sup>TM</sup> III family devices uses dedicated input pins that are sampled during the assertion of reset to configure the processor. The master reset signal is generated locally on-board from the reset circuitry, controlled by the System CPLD, as shown in Figure 5-8.

Figure 5-8. MPC8572E POR Configuration

All of the POR configuration signals are handled via System CPLD control. Some of the MPC8572EAMC signals are changeable via a set of DIP switches, whereas others are physically hard-wired on the board to minimize board space. Some of these signals have an internal pull-up that selects a default state. Table 5-7 details all POR configuration pins and their specific usage on the MPC8572EAMC board.

| POR Usage               | Functional Pin<br>(Reset Configuration Name)                                              | Chip<br>Default | Board<br>Setting | Board Setup Description                 | Control<br>Method |

|-------------------------|-------------------------------------------------------------------------------------------|-----------------|------------------|-----------------------------------------|-------------------|

| System PLL Ratio        | LA[29:31]<br>(cfg_sys_pll[0:2])                                                           | None            | 100              | CCB Clock: SYSCLK Ratio = 10:1          | DIP Switches      |

| e500 Core0 PLL<br>Ratio | LBCTL, LALE, LGPL2<br>(cfg_core0_pll[0:2])                                                | None            | 100              | E500 Core0: CCB Clock Ratio = 2:1       | DIP Switches      |

| e500 Core1 PLL<br>Ratio | LWE[0], UART_SOUT[1],<br>READY_P1<br>(cfg_core1_pll[0:2])                                 | None            | 100              | E500 Core1: CCB Clock Ratio = 2:1       | DIP Switches      |

| DDR PLL Ratio           | TSEC_1588_CLK_OUT,<br>TSEC_1588_PULSE_OUT1,<br>TSEC_1588_PULSE_OUT2<br>(cfg_ddr_pll[0:2]) | None            | 100              | DDR Complex CLK: DDRCLK<br>Ratio = 10:1 | DIP Switches      |

| Boot ROM location       | TSEC1_TXD[6:4],TSEC1_TX_ER<br>(cfg_rom_loc[0:3])                                          | 1111            | 1111             | Local Bus GPCM 32-bit ROM               | DIP Switches      |

Table 5-7. MPC8572E POR Configuration DEFAULT Settings

| POR Usage                                  | Functional Pin<br>(Reset Configuration Name)         | Chip<br>Default | Board<br>Setting | Board Setup Description                                                                          | Control<br>Method                                                |

|--------------------------------------------|------------------------------------------------------|-----------------|------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Host/Agent Config.                         | LWE[1:3]/LBS[1:3]<br>(cfg_host_agt[0:2])             | 111             | 111              | MPC8572E is root complex/ Host processor for all interfaces                                      | DIP Switches                                                     |

| I/O Port Selection                         | TSEC1_TXD[3:1],TSEC2_TX_ER<br>(cfg_IO_ports[0:3])    | 1111            | 1100             | Serial RapidIO x4 (3.125 Gbps),<br>125-MHz reference clock                                       | DIP Switches                                                     |

| CPU Boot<br>Configuration                  | LA27,EC3_MDC<br>(cfg_cpu0_boot, cfg_cpu1_boot)       | 11              | 10               | Core #0 allowed to boot without<br>waiting for external master; core<br>#1 held in boot hold-off | DIP Switches                                                     |

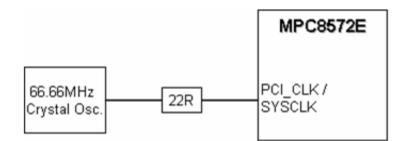

| Boot Sequence<br>Config.                   | LGPL3,<br>LGPL5<br>(cfg_boot_seq[0:1])               | 11              | 11               | Boot sequencer is disabled. No<br>I <sup>2</sup> C ROM is accessed                               | DIP Switches                                                     |