QorlQ Qonverge Platform

# QorlQ Qonverge BSC9131 Reference Design Board

Single-chip solution for femtocell base stations, VoIP gateways, video processing and industrial automation

#### Overview

The QorlQ Qonverge BSC9131 reference design board (BSC9131RDB) enables the development of applications in the wireless base station, military and aerospace, enterprise and industrial markets. The reference design board is housed inside a standard mini-ITX enclosure, and exposes a GPS antenna connector, serial RS232 connector, TDM port, USB interface and two Gigabit Ethernet ports with support for 1588v2 for fast prototype designs. The BSC9131RDB allows for verification of the QorlQ Qonverge BSC9131 processor operation and enables end-to-end system performance verification.

Within the wireless base station market, the BSC9131RDB supports the development and testing of the Layer 1, Layer 2 and Layer 3 protocol stacks, as well as higher layer wireless software applications. The highly integrated BSC9131 SoC targets the evolving small cell base station market and combines the e500 Power Architecture® CPU and StarCore SC3850 DSP with MAPLE-B2F baseband acceleration processing elements. Together, they address the need for a high-performance, cost-effective, integrated solution that handles all required processing layers without the need for additional external processing devices.

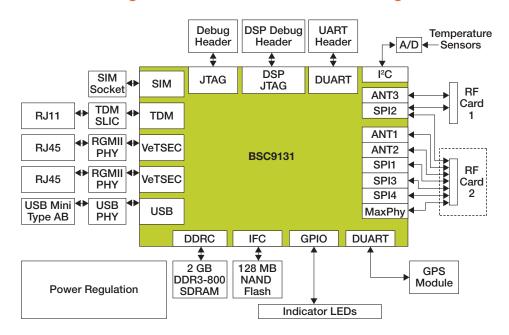

## QorlQ Qonverge BSC9131 RDB + RF Block Diagram

### **Target Applications**

- Wireless infrastructure: 32-user eNodeB femtocell base stations

- Radio communications systems

- Test equipment: Network simulators for 3G and 4G technologies

- VoIP gateways/PBX

- Software-defined radio

- Video processing

- Industrial automation

At the heart of this development system is the BSC9131 SoC, featuring:

- High-performance 32-bit e500 core built on Power Architecture technology

- o 36-bit physical addressing

- o Double-precision floating-point support

- 32 KB L1 instruction cache and

32 KB L1 data cache

- Enhanced hardware and software debug support

- o 800 MHz to 1 GHz clock frequency

- 256 KB L2 cache with ECC, also configurable as SRAM and stashing memory

- One StarCore SC3850 core subsystem, which connects to the following:

- o 32 KB 8-way L1 instruction/data cache

- 512 KB 8-way L2 unified instruction/ data cache

- · Memory management unit

- Enhanced programmable interrupt controller

- o Debug and profiling unit

- o Two 32-bit timers

### **Specifications**

| Processor             | One e500 processor built on Power Architecture technology and 256 KB shared L2 cache. StarCore SC3850 DSP subsystem, including 512 KB private L2 cache. |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 V DC Power         | 12 V DC @ 5.5 A, 100-240 V AC input                                                                                                                     |

| Ethernet (WAN)        | RJ-45 jack                                                                                                                                              |

| Memory                | One bank of 2 GB DDR3, 128 MB NAND flash                                                                                                                |

| SIM Card              | 1.3/3.8 V                                                                                                                                               |

| Ethernet (Local Net)  | RJ-45 jack                                                                                                                                              |

| VoIP Handset          | RJ-11 jack                                                                                                                                              |

| USB                   | Mini-AB socket                                                                                                                                          |

| GPS Antenna           | SMA or MCX female                                                                                                                                       |

| RF Card 1 Antenna(s)  | Dual SMA female                                                                                                                                         |

| RF Card 2 Antenna(s)  | Dual SMA female                                                                                                                                         |

| Operating Temperature | 0 °C to 40 °C, Humidity 5% to 95% RH                                                                                                                    |

| Storage Temperature   | -20 °C to +70 °C (-4 °F to +158 °F)                                                                                                                     |

- Multi Accelerator Platform Engine (MAPLE) for femtocell base stations

- Baseband processing (MAPLE-B2F)

- Supports variable sizes in Fourier transforms, convolution, filtering, turbo, Viterbi and chiprate

- Consists of accelerators for UMTS chip rate processing, LTE UP/DL channel processing, matrix inversion operations and CRC algorithms

- DDR3/DDR3L SDRAM memory controller supports 16-bit with ECC and 32-bit without

- Rich set of peripherals perfectly suited for residential femtocell applications

#### **Features**

- High-performance QorlQ Qonverge BSC9131 integrated SoC with Power Architecture technology and StarCore DSP

- End-to-end development system for LTE-FDD/TDD, WCDMA (HSPA+) and CDMA2K, including the RF module for LTE and WCDMA (HSPA+) technologies (provided separately)

- Simultaneous dual mode operation, such as LTE-FDD + WCDMA (HSPA+)

- FCC certified TDM Interface

- Rich ecosystem with partners in OS, modem protocol stack and RF transceivers

- VortiQa software for enterprise equipment optimized for multicore processors

# For more information about the QorlQ Qonverge platform, visit freescale.com/QorlQQonverge

Freescale, the Freescale logo, QorlQ Qonverge and StarCore are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2012, 2014 Freescale Semiconductor, Inc.

Document Number: PSC9131RDBFS REV 3